(中国电子科技集团公司第三十研究所,四川 成都610041)

摘要:随着国产处理器的功能和性能的提升,越来越多的行业设备采用搭载国产处理器的计算机主板。在恶劣环境应用场景下,主板内存设计采用更可靠的板载颗粒的方案,而国产单片内存颗粒的最大容量有限,采用双Rank内存设计增大访问内存的容量。在这种情况下,尺寸较小的主板的器件布局和PCB布线都提出了更高的要求,高密度布线对DDR信号干扰更加明显。本文提出了一种基于国产处理器的板载双Rank内存设计与仿真优化的方法,通过对影响内存信号质量的关键因素的分析,实现对信号完整性的仿真分析和优化,从而在实现更大内存容量的同时,节省了PCB设计时间和开发成本,实现更可靠稳定的内存访问控制。

关键词:国产处理器;双Rank,内存设计,仿真优化

1概述

近年来,中美双边贸易摩擦日益加剧,对我国芯片行业的发展带来巨大影响。国内涌现出大量半导体设计和制造相关公司,研发的芯片包括中央处理器、桥片、内存、FPGA、DSP和电源芯片等。采用国产自主处理器和内存设计的主板越来越多,国产处理器的运行速度越来越快,对存储器的数据传输能力要求也越来越高,在有限电路板尺寸下高速电路的互连关系变得越来越复杂,PCB设计也越来越复杂。为了降低重新制版造成的产品交付进度风险和成本风险,解决板卡复杂信号完整性,设计过程增加了仿真要求,根据仿真结果对设计进行优化。

在设计的不同阶段通过仿真来指导优化设计,PCB设计初期做前仿(pre-simulation),PCB完成设计做后仿(post-simulation)。本文主要针对PCB前仿和后仿两个阶段,介绍了仿真的一些基础理论和PCB设计规则,对双Rank DDR的信号质量及时序进行仿真,提升高速设计的信号完整性。

2仿真分析

本例使用的仿真软件是Cadence SPB 16.6/Allegro Sigrity 2017,采用双Rank板载DDR颗粒设计,16片16bit颗粒,800M的数据信号速率。在设计双Rank DDR时,单端信号(ADDR/CMD/CTRL)的终端匹配电阻在40~60Ω之间,并且上拉到VTT,上拉电阻要根据不同阻值的SI仿真的结果来选择,国产处理器通常在20~40Ω之间,差分信号(CLK)的阻抗匹配电阻为100Ω。可以对印制板叠层、传输线和过孔的各项参数进行设计、仿真优化,达到降低信号的反射、过冲和串扰等问题。结合实际产品要求,与印制板厂商沟通制板要求,同时考虑性价比和加工周期,这就是前仿的过程。

后仿主要针对拓扑结构的信号反射的仿真,通过仿真确定信号的电路结构、走线阻抗、匹配阻容的大小以及各pin-pair的布线长度。同时,DDR采用了新的技术—ODT ( On-Die Termination ),即芯片内部匹配终结技术。所谓ODT,是在DRAM内部有终端电阻,DRAM是主动的状态的时候启动ODT,是待机状态的时候关闭ODT。根据这个,能降低信号的反射,提高信号质量,降低功耗。最适合的终端电阻器的验证就要通过拓扑仿真才能完成。

3仿真测试

3.1前仿真

针对DDR的数据和地址/命令信号,两个Rank的方式进行DDR设计,每个Rank包含4片DDR颗粒,每个控制器共连接了8片DDR颗粒,布线密度更大。两个Rank的方式不同于以往的DDR设计,因此对其信号质量进行前仿真。

3.1.1数据信号

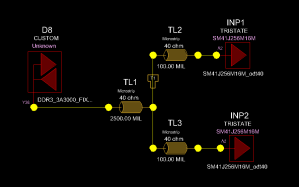

数据信号(DQ/DM/DQS)为T型拓扑,不再是常规的点到点拓扑结构,T型拓扑结构相对来说布线等长会比较好设计。以数据信号DQ为例,拓扑结构如图 1所示。

图 1 2个Rank方式DQ信号拓扑结构

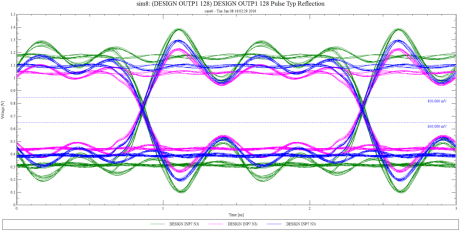

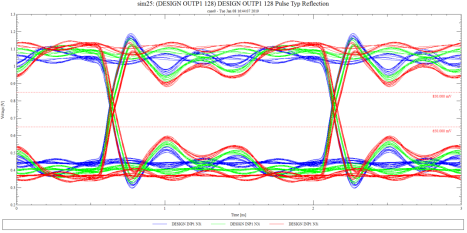

由于数据信号为双向信号,所以拓扑仿真要对读写两个方向进行仿真,即写方向3A3000到SM41J256与读方向SM41J256到3A3000。当驱动端内阻、传输线阻抗、ODT端接都是40欧姆时,没有反射影响。但当拓扑结构中的传输线阻抗、ODT端接电阻值等各不相同时,信号质量也会有所差异。不同驱动能力和ODT参数的情况下,读、写操作的眼图仿真结果如图 2、图 3所示。

图 2 写操作的眼图

图 3 读操作的眼图

从仿真结果的信号波形可以看出:写方向不同驱动能力和ODT端接的波形几乎没有差异;读方向不同驱动能力和ODT端接的波形有所差异。通过拓扑仿真得出结论:传输线的主干段阻抗选择40Ω,分支线的阻抗为60Ω,控制器及DDR的驱动能力、ODT参数按表 1所示参考配置。

表 1 控制器及DDR的参数

操作 | 控制器 | DDR(Active) | DDR(Standby)ODT | 备注 | ||

驱动 | ODT | 驱动 | ODT | |||

写操作 | 34/40Ω | -- | -- | 60/120Ω | 60/120Ω | DDR的ODT可固定设置为一个值 |

读操作 | -- | 60Ω | 34/40Ω | -- | 60/120Ω | |

3.1.2地址/控制信号

由于采用了2个Rank的方式,ADDR信号基本上无法使用传统的Fly-by拓扑结构,而是使用Fly-by与T型相结合的拓扑结构,ADDR拓扑结构如图 4所示。该拓扑结构兼顾了良好的等长控制和较好的噪声处理,能更好地保证信号的完整性。

图 4 ADDR拓扑结构

图 5 阻抗及端接为40Ω的仿真结果

控制器的输出阻抗、传输线阻抗以及末端的端接匹配电阻均设置为40Ω时,仿真结果如图 5所示。离控制器越近的DDR信号质量越差,在实际电路中,考虑到电源噪声、串扰等因素影响时,信号质量会进一步恶化,因此必须对阻抗和端接电阻进行调整。当驱动为20Ω、分支阻抗为60Ω、端接27Ω时,眼图的眼高指标最好,此时的仿真结果如图 6所示,但此时距控制器最远的两片DDR颗粒信号的振铃X现象比较明显。保持分支阻抗为60Ω、端接27Ω,驱动能力设置为20Ω、30Ω、40Ω后的对比如图 7所示,驱动内阻越大振铃幅度越小。保持驱动能力为40Ω,分支阻抗为60Ω、端接设置为27Ω、33Ω、40Ω后,前两片DDR颗粒的对比如图 8所示,端接电阻越小信号质量越好。

图 6 驱动20Ω分支60Ω端接27Ω的仿真结果

图 7 不同驱动能力下最后两片DDR的仿真结果

图 8 不同端接电阻时前两片DDR的仿真结果

根据眼图仿真结果,并综合考虑功耗、EMC等因素,推荐传输线的主干段阻抗选择40Ω,分支线的阻抗为60Ω,控制器的驱动能力选择30Ω或40Ω,端接电阻选择27Ω。

3.2后仿真

当完成所有DDR信号的拓扑仿真,验证信号的电路结构满足DDR的信号完整性要求,就可以在PCB设计软件中为DDR信号设置约束。对于单独的信号需要设置信号的最小/最大传输延时,而对DDR系统中每一组Byte Lane中的各个信号需设置信号之间的相对传输延时。约束设置和完成布线之后,就要板级后仿真验证工作。板级后仿真主要是进行DDR信号完整性和时序关系的验证。首先,确定DDR源同步信号组及其相关的Clock/Data Strobe信号;然后,在仿真软件中建立总线,设定仿真模型以及仿真码流;最后,通过仿真建立的总线信号,测量相关的参数来验证布线是否合理。

由于DDR的设计较为成熟,本例仅针对2个Rank形式的3A3000和国产内存颗粒,选择其中一个控制器进行数据和地址的时序仿真。其中数据组的拓扑结构为4组T形结构,对其中一组进行了仿真。

3.2.1数据信号

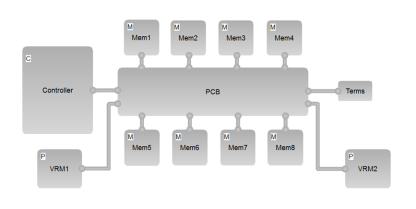

根据DDR数据信号的时序关系,将3A3000的MC1控制器对应的数据信号分为Data0~Data7共8个组,其中Data6和Data7组的信号连接关系如图 9所示,仿真时数据组的系统拓扑如图 10所示,两片Memory中有一片为Active状态,另一片为Standby状态。

图 9 MC1的Data6和Data7数据组

图 10 仿真时数据组的系统拓扑

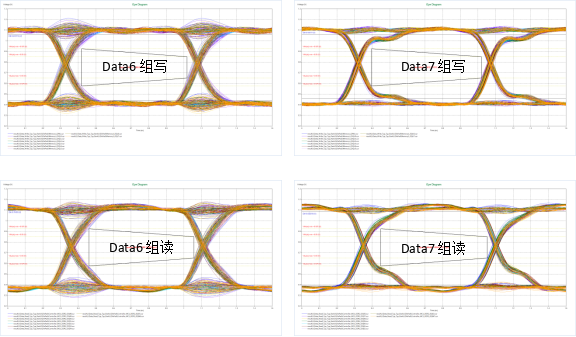

设置驱动能力为34Ω/40Ω、ODT值设置为60Ω/120Ω,各参数下的DDR读写眼图仿真结果如图 11、图 12、图 13所示,眼图均满足要求。驱动能力为40Ω、ODT为60Ω时眼图的眼宽和眼高最小,但此时的高频分量较少,上下眼皮较细;提高驱动能力或提高ODT阻抗都会使眼宽和眼高增大,但同时会引入较多的高频分量,出现了“双眼皮”。

图 11 34Ω驱动60ΩODT时数据组的眼图

图 12 40Ω驱动60ΩODT时数据组的眼图

图 13 40Ω驱动120ΩODT时数据组的眼图

3.2.2地址信号

3A3000的MC1控制器对应的地址/命令信号连接关系如图 14所示,仿真时地址/命令信号的系统拓扑如图 15所示。

图 14 MC1的地址/命令信号

图 15 仿真时地址/命令信号的系统拓扑

设置控制器的驱动能力为40Ω,端接电阻分别为40Ω、33Ω、27Ω时,随着端接阻值的减小,Mem1的眼高逐渐增大,Mem4的眼高逐渐减小。端接值为27Ω时,Mem1~Mem4的眼高较为一致,总体信号质量较好。Mem1和Mem4在三种端接电阻时的眼图对比如图 16、图 17所示。

图 16 Mem1不同端接时的眼图对比

图 17 Mem4不同端接时的眼图对比

4结束语

基于国产处理器的双Rank内存设计中,不同传输线阻抗、驱动能力和ODT端接都会影响内存信号质量。本文通过仿真软件进行前仿真和后仿真,根据仿真结果确定了内存信号有关参数,完成了不同参数下信号眼图效果对比,最终确定了最优参数范围,满足产品指标要求。通过仿真分析大大节省了板卡设计的时间,同时也保证了产品的质量。尤其是在高速电路设计中,不论是研发阶段的前仿,还是测试阶段的后仿,仿真分析都显得尤为重要,也是增强高速电路板设计可靠性和稳定性的必要手段。

参考文献

[1]Howard Johnson, Martin Graham. 高速数字设计. 沈立, 朱来文, 陈宏伟等译. 北京 : 电子工业出版社, 2004.5.

[2]Stephen H. Hall, Garrett W. Hall, James A. McCall. High-Speed Digital System Design [M]. New York: John Wiley & Sons Inc. 2000.

[3]JESD79-3F, DDR3 SDRAM Standard. USA: JEDEC 2012.

[4]吴均,周伟,陈德恒. 高速电路设计仿真实战——信号与电源完整性. 武汉 : 华中科技大学出版社, 2019.9.

[5]周润景. Cadence 高速电路板设计与仿真(第4版)——原理图与PCB设计. 北京 : 电子工业出版社, 2011.7.

作者简介:

吴帮强(1986—),男,学士,工程师,主要研究方向为高速数字电路设计、电磁兼容与EDA仿真分析设计;

张晓雄(1979—),男,硕士,高级工程师,主要研究方向为高速数字电路设计、信号/电源完整性分析;

杨希梅(1976—),女,大专,工程师,主要研究方向为高速数字电路设计与EDA仿真分析设计;

陈明波(1983—),男,硕士,工程师,主要研究方向为高速数字电路设计、电磁兼容与EDA仿真分析设计。

1