天津七六四通信导航技术有限公司 天津市 300210

摘要:在数字电路系统中,复位是一个非常重要的功能,它常常决定了该电路是否能正常启动,电路中的程序是否能正常运行。讨论了常见的实现复位功能的方式,每种方式的实现手段,以及这些方式各自的优缺点。

关键词:数字电路;复位功能;设计

引言

复位电路是数字系统设计中十分关键的环节,处理不当会产生亚稳压现象,影响系统的稳定性。复位电路的主要目的是迫使电路回到一个确定的状态。由于数字系统中含有大量的触发器和寄存器,每个触发器和寄存器都需复位,因此复位电路的设计成为整个系统设计的关键问题所在。复位电路分为同步复位和异步复位两种方式。同步复位是相对同步输入信号而言,需要时钟信号的作用,设计较容易;异步复位不需要考虑时钟信号,独立作用于触发器和寄存器的复位端,但是异步复位的静态时序分析复杂度较高,而且会使电路产生亚稳态现象。

1常见的复位方式

常见的复位方式有如下四种:上电复位、手动复位、看门狗复位和软件复位。上电复位:电路上电期间件执行的复位,决定电路是否能正常启动。手动复位:利用电路中的按键来产生复位信号,从而令电路复位的方式。常常用于调试或令系统从异常状态下人工重启恢复。看门狗复位:利用看门狗定时器设定一段时间,该时间段内刷新信号正常则系统正常工作,若超过时间没有信号刷新,则产生复位信号重启系统。常用于令系统从异常状态下自动重启恢复。软件复位:利用处理器提供的复位指令或软件复位控制位进行复位。是一种由软件开发人员利用程序产生的复位。是处理器的一种内嵌功能。

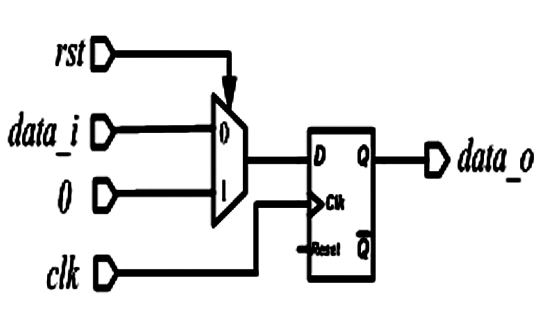

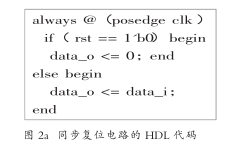

2同步复位电路

同步复位是指复位信号仅在时钟信号有效沿到来时才对寄存器复位,因此复位信号被认为是寄存器的一个输入信号,电路结构如图1所示。从图1可以看到同步复位电路没有使用寄存器的Reset(复位)端口,电路只是把复位信号rst作为数据选择器的控制端口,如果低电平复位,就在电路的有效沿将“0”作为寄存器的输入,反之亦然。同步复位电路的HDL代码如图2a所示,利用ALTERA公司的QuartusII6.0软件得到的功能仿真如图2b所示。同步复位的优点在于复位信号只在时钟信号clk的有效沿触发来判断电路是否复位,确保整个系统采用同步设计,这大大降低了亚稳态出现的概率。同步复位的缺点在于电路需要更多的逻辑资源来实现,如图1所示;此外,由于同步复位需要额外的逻辑资源,因此同步复位复位时间缓慢。

图1a低电平同步复位电路结构图

图1b高电平同步复位电路结构图

图2b同步复位电路的功能仿真

3基于复位管理芯片的多功能复位电路设计

在一些对稳定性和复位功能要求较高的场合,我们可以利用复位管理芯片来实现电路的复位功能。下面,就以美信公司的MAX813为例来介绍这类复位电路的设计。MAX813能够产生200ms的上电复位脉冲,实现手动复位和看门狗复位功能。同时,还提供电源的低电压检测及复位功能。MAX813共有8个引脚,其功能简述如下:脚1(/MR):手动复位信号输入引脚。当该引脚的输入电平低于0.8V时,芯片输出复位信号;脚2(VCC):+5V电源输入端;脚3(GND):电源地引脚。脚4(PFI):低电压检测输入引脚。当该引脚输入电压低于1.25V时,脚5(/PFO)输出低电平。若不使用该检测功能,将其与GND或VCC相连即可。脚5(/PFO):低电压检测输出引脚。当脚4(PFI)的输入电平低于1.25V时,输出低电平。脚6(WDI):看门狗刷新信号输入端。当该引脚的电平在1.6S内发生变化时,WDO输出低电平。否则,WDO将输出高电平。如果不使用看门狗复位功能,将该引脚悬空即可。脚7(RESET):高有效复位电平输出端。脚8(/WDO):看门狗信号输出端。基于MAX813设计的基本复位电路如图2所示。该电路具有上电复位,看门狗复位,低电压检测这三项功能。上电复位功能为片本身的特性。只要芯片一加电,复位引脚就会输出一个200ms的复位脉冲。看门狗定时器的输入引脚WDI接到处理器芯片的一个通用I/O引脚上,由程序控制,定时刷新。如果系统死机或程序跑飞,WDI引脚将无法在规定的1.6s时间内得到刷新。这样,WD0引脚将输出一个低电平。如图所示,WD0引脚接到了芯片的手动复位输入端。因此,WD0引脚输出一的个低电平就会触发一个手动复位,在复位引脚输出有效的复位脉冲。本电路对系统中的12V直流电压进行监测。当电压降低,导致PFI的电平低于1.25V时,PFO引脚将产生一个低电平。这个低电平通过处理器芯片的一个通用I/O引脚进入处理器内部,通常可通过程序查询处理。如果要提高响应速度,可将PFO引脚接入处理器芯片的外部中断来进行处理。

基于MAX813设计的复位电路

结语

本文介绍了两种复位电路的设计。简单复位电路设计难度低、成本低廉,但抗干扰能力和驱动能力较差。基于复位管理芯片设计的多功能复位电路,成本较高,设计难度大一些,但稳定性,可靠性,驱动能力较好。电路设计时可依据具体的应用环境进行选择。

参考文献

[1]张毅刚,彭喜元,彭宇,单片机原理及应用[M].北京:高等教育出版社,2009.

[2]CliffordE.Cummings,DonMills.“Asynchronous&SynchronousResetDesignTechniques”,PartDeux[C]SNUG,2003:15-17.